## Factsheet RapidIO<sup>™</sup> - SI11RI10

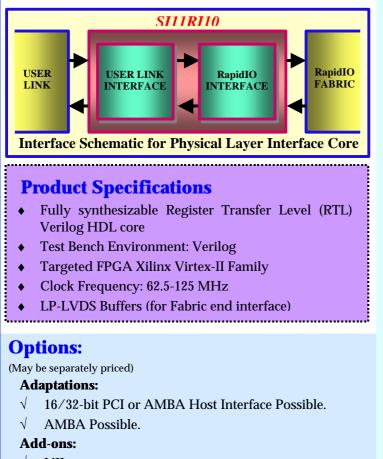

### **Physical Layer Interface Core**

Silicon Interfaces<sup>®</sup> RapidIO<sup>TM</sup> is a packet-switched interconnect intended primarily as an intra-system interfaces for a chip-to-chip and board-to-board communications at Gigabyte-per-second performance levels. Developed as an open standard, the RapidIO<sup>TM</sup> architecture addresses the needs of present and future systems. RapidIO<sup>TM</sup> is focused as a processor, memory and memory mapped I/O interfaces optimized for use inside the chassis.

This high performance low pin-count packet switched system level interconnect provides highly reliable error handling scheme whilst transferring packets between processing elements via the RapidIO<sup>™</sup> Fabric.

In the diagram below, the User Application sends data in chunks of 32 bits to the core, which composes and queues the packets in the RapidIO<sup>TM</sup> format, before transmission to the Fabric. Similarly, the Fabric sends RapidIO<sup>TM</sup> packets to the chip, which in turn queues and sends data to the User Application via a Microcontroller Interface.

$\sqrt{NIL}$

# Silicon Cores<sup>™</sup>

#### **Core to the Intelligent System**<sup>T</sup>

### **Product Highlights**

- ✓ Fully Compliant with RapidIO<sup>™</sup> Interconnect Specification Rev 1.1, 3/2001 prescribed by RapidIO<sup>™</sup> Trade Association.

- ☑ 32-bit standard Host/Link Interface.

- ☑ **Full Duplex** Independent Transmit and Receive Data Path.

- Dual Data Rate (DDR): 62.5-125 MHz.

- $\blacksquare$  Auto scaling 8/16 bit Ports.

- ☑ Respects 32-bit boundaries.

- ☑ **Rx Queuing**: 16 X 128 X 32 or 8 Kbytes of internal buffer.

- ☑ **Tx Queuing**: 8 X 128 X 32 or 4 Kbytes of internal buffer.

- ☑ Maximum Packet Length: 276 bytes.

- ☑ Minimum Packet Length: 8 bytes.

- ☑ Supports a Very Highly Reliable Error Handling Scheme.

- ☑ CRC-16 Polynomial.

- ☑ Incorporates Intermediate CRC for Packet Length of 80 bytes or greater.

- ☑ Upto 8 Unacknowledged Packets.

- ☑ 32-Bit Internal Data Path.

- ☑ Supports: **PACKET RERTY**, **PACKET NOT ACCEPTED**, **STOMP**, **TIME-OF-DAY SYNCHRONIZATION**, **TRAINING** and **THROTTLE**.

- $\begin{tabular}{|c|c|c|c|c|} \hline $M$ an agement & Interface \\ (CSRs/CARs). & \end{tabular}$

- ☑ Data Rate 250-500 Mbps per LVDS Pin Pair; Upto 8 Gbits per sec throughput.

- ☑ Outputs 32-bits of Data to User Interface.

- $\blacksquare$  Full Control of User Interface bus by user.

- ☑ Tx and Rx sections designed for minimum latency between the input and output.

- ☑ Smart Bandwidth Utilization (Designed for minimum latency between Link and Fabric, Intelligent EOP avoidance between Back-to-Back Packets).

- ☑ **Fully automated** Test Bench for checking for error-free packets.

- ☑ 3 Clock Domains 1 for Management, 2 for Fabric and Link Interface.

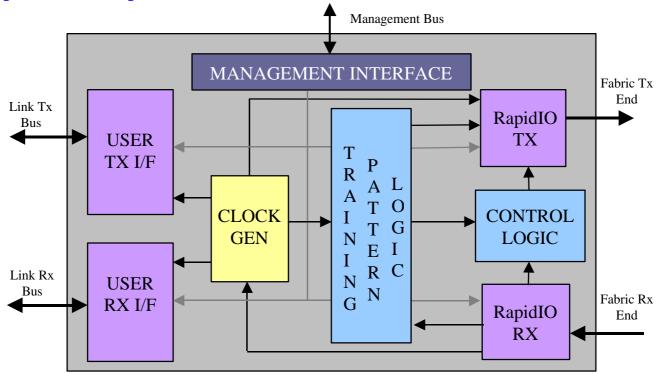

#### **RapidIO Block Representative Schematic:**

- <u>RapidIO RX</u>: Comprises Frame Detect module to detect toggling of received frame signal and CRC-16 Checker to check the authenticity of received packets. The Receive Buffer Control Logic controls the transfer of data onto the on-chip Receive Queue. The capacity of the Receive Queue is 16 x 128 x 32 bits.

- User RX Interface: It provides Data to User Link, which is basically a 32-bit Microcontroller interface.

- <u>User TX Interface</u>: Accepts 32 bits of data from the User Link and transmits the same to the Transmit Queue, which is an on-chip block RAM bearing a capacity of 8 x 128 x 32 bits.

- <u>RapidIO TX</u>: Contains Transmit Control logic to pick up data from TX Queue and transmit over to RapidIO<sup>™</sup> bus. It also squeezes in Control Frames as and when necessary. This section also contains CRC Generator, Transmit Control, Transmit Frame Generator and the Transmit Queue. Data from queue is picked up by the Transmit Control logic and transmitted over RapidIO<sup>™</sup> Transmit Bus, tdata [0:31], in compliance with RapidIO<sup>™</sup> standard.

- <u>Control Logic</u>: This module strips and decodes the various Control Symbols transmitted from the **RapidIO™ Fabric**, as well as generates Control Symbols to be transmitted over to the Fabric.

- <u>**Training Pattern Logic**</u>: This block is responsible for decoding and transmitting **Training Patterns** immediately after chip initialization and as and when required by the adjacent Processing Element across the Fabric. Upon Reset, communication with the Fabric is possible only after the successful completion of the **Training Sequence**.

- <u>Management Interface</u>: The Management Interface is mainly responsible for writing/reading to/from CARs (Capability Registers) and CSRs (Command and Status Registers). A totally independent interface has been provided for the same.

#### **Contact:**

Email: info@siliconinterfaces.com Phone: (+91-22) 2491 3024; Fax: (+91-22) 2498 1379 In USA: (+1-408) 866 2458; Fax: (+1-408) 866 6586 In UK: (+44-20) 8543 4436; Fax: (+44-20) 8544 1311

**Notice:** Information in this document is indicative. Product specifications are subject to change without notice. *Silicon Interfaces* shall not be responsible for direct, indirect or consequential damages that may accrue through typographical errors or otherwise. No license, expressed or implied to any intellectual property rights is granted by this document. Product names mentioned herein may be trademarks and/or registered trademarks of their respective owners. Rights are hereby acknowledged.

a software and vlsi design center

Silicon Interfaces is the world's answer to integrated solutions for Design Services needs for SOC, ASIC & FPGA for Wireless, Cable & Optical Networking, Fiber Channel & Inter-connect, Data Communications and Storage. Silicon Interfaces is operating since 1990 primarily in USA, Europe and Pacific Rim.

RI1.0 12/20/2002

Copyrights © 2002-2003 *Silicon Interfaces* Private Limited. All rights reserved. 606, Nirman Kendra, E. Moses Road, Mahalaxmi, Mumbai 400 011 India www.siliconcores.com and www.siliconinterfaces.com